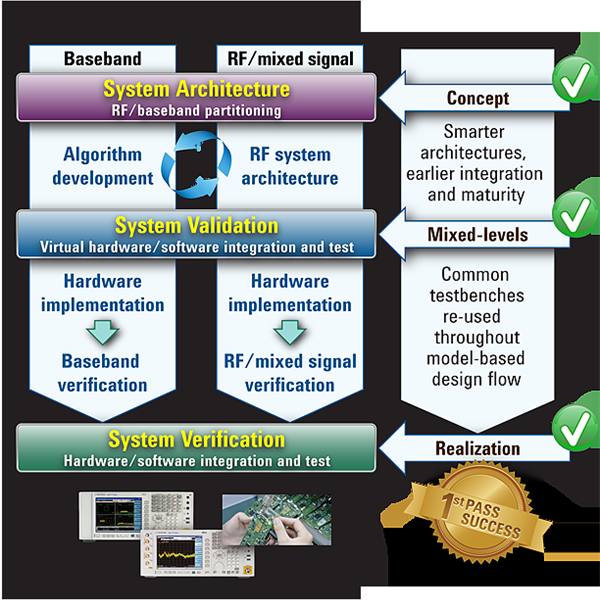

Simplifying low-power SoC top-down design using the system-level abstraction and the increased automation - ScienceDirect

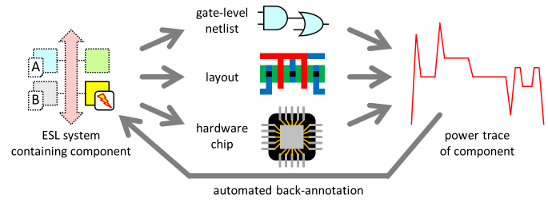

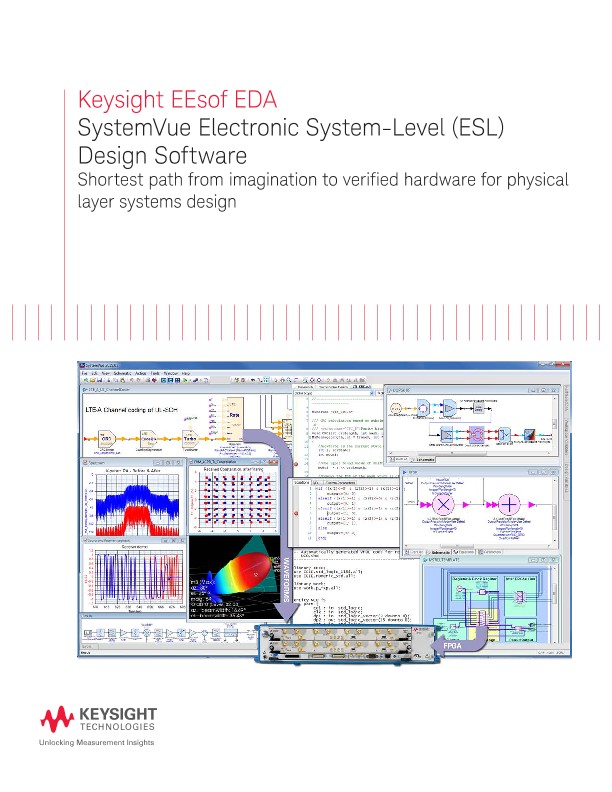

Institute for Communication Technologies and Embedded Systems: Power Estimation at Electronic System Level

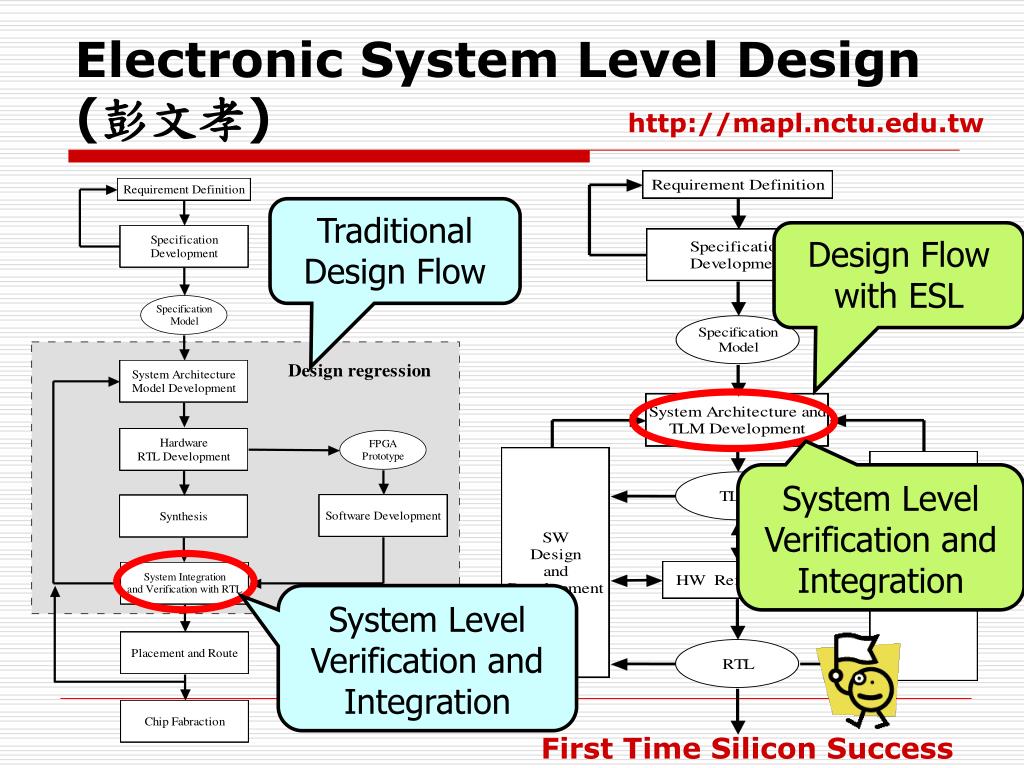

![PDF] An electronic system level modeling approach for the design and verification of low-power systems-on chip. (Une approche de modélisation au niveau système pour la conception et la vérification de systèmes sur PDF] An electronic system level modeling approach for the design and verification of low-power systems-on chip. (Une approche de modélisation au niveau système pour la conception et la vérification de systèmes sur](https://d3i71xaburhd42.cloudfront.net/aa552235ed329e4988af2e89c9f0444356d26667/53-Figure2.1-1.png)

PDF] An electronic system level modeling approach for the design and verification of low-power systems-on chip. (Une approche de modélisation au niveau système pour la conception et la vérification de systèmes sur

![The IC Industry - Essential Electronic Design Automation (EDA) [Book] The IC Industry - Essential Electronic Design Automation (EDA) [Book]](https://www.oreilly.com/api/v2/epubs/0131828290/files/0131828290_app06lev1sec1_image01.gif)